The semiconductor industry is always striving for miniaturization. But miniaturization presents the problem of energy inefficiency in silicon based semiconductor technology. Carbon nanotubes (CNT) have been touted as next best semiconductor technology that could facilitate energy efficient miniaturization.

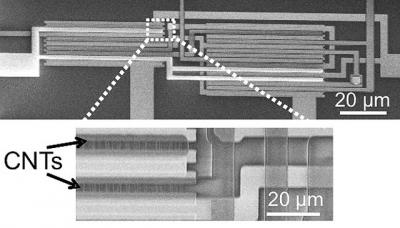

VLSI circuits with Carbon nanotubes (Credit: Stanford University School of Engineering)

Carbon nanotubes are cylindrical nanoscale carbon structures with extraordinary thermal, electrical, and mechanical properties. The CNT in their basic form, have existed since 1998 and have shown promise in supporting advanced, highly efficient electronics. However, the material flaws characteristic of nanotubes have rendered CNTs unviable. The Stanford team, led by Professors H.-S. Philip and Subhasish Mitra, has been working to overcome the limitations of CNTs and have achieved significant breakthroughs.

The important achievements of CNT circuits have mostly been restricted to single nanotube level. This is due to the difficulties involved in employing CNTs in practical applications. The first challenge is the inability to align the CNTs suitably, which gives rise to stray conducting paths in the circuit apart from causing faulty connections. The second problem is the presence of metallic CNTs. This is due to the inability to synthesize pure semiconductor nanotubes. As a result, the circuits are characterized by short circuits, susceptibility to noise and power leakage. The Stanford team’s design for circuits takes the placement variability and electrical properties into consideration. Their design not only helps retain the energy efficiency of CNTs, but is also compatible with current fabrication techniques, thereby making it economically viable.

The Stanford engineers have demonstrated their technique by developing sequential storage and arithmetic circuits and a monolithic 3D integrated circuit.

Source: http://engineering.stanford.edu/

Disclaimer: The views expressed here are those of the author expressed in their private capacity and do not necessarily represent the views of AZoM.com Limited T/A AZoNetwork the owner and operator of this website. This disclaimer forms part of the Terms and conditions of use of this website.